# **RAIO**

## **RA8889**

## TFT LCD 文字图形控制器

规格书

July 7, 2020

RAiO Technology Inc.

©Copyright RAiO Technology Inc., 2020

## 1. 简介

RA8889 支持 CMOS 准位的接口 ,规格书内包含: 系统方块图、引脚图、AC/DC 电气特性、各个功能子方块、寄存器、省电模式的详细描述。

#### 1.1 概况

RA8889 是一款低功耗及顯示功能強大的彩色 TFT 控制器,內部具有記憶體 SDRAM,為了可以快速為顯示記憶體進行螢幕更新,RA8889 支持 MCU 端 8080/6800 8/16-bit 非同步並列介面與 3/4 線 SPI 及 IIC 串列介面,提供多段的顯示記憶體緩衝區段,並提供畫中畫 (PIP)、透明度控制與顯示旋轉鏡像及內建 JPEG Decoder 等功能。

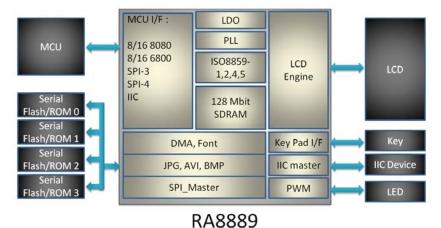

#### 1.2 系统与芯片示意图

MAGGGG

Figure 1-1: System Diagram

#### 2. 特性

#### 2.1 图框缓冲区

● 内建 128Mb SDRAM

#### 2.2 主控端接口

- 支持 8080/6800 8/16-bit 异步并列接口

- 对于扩展的 MPU 周期提供 Xnwait 的信号以供交握

- 支持串行主控端接口,例如. IIC, 3/4-wire SPI

- 对于图像数据写入支持镜像与旋转的功能

#### 2.3 输入显示数据格式

- 1bpp: 单色 (1-bit/像素)

- 8bpp: RGB 3:3:2 (1-byte/像素)

- 16bpp: RGB 5:6:5 (2-byte/像素)

- 24bpp: RGB 8:8:8 (3-byte/像素或 4-byte/像素)

- Index 2:6 (64 索引色/像素并带透明度属性)

- αRGB 4:4:4:4 (4096 索引色/像素并带透明度属性)

- αRGB 8:8:8:8 (8 bit alpha, 24bpp 色深)

#### 2.4 显示模式

● 使用者可以设定 24/18/16-bit TFT 显示输出方式

#### 2.5 支持多种屏幕分辨率

- 支持 16/18/24-bit CMOS 接口屏幕

- 支持屏幕分辨率最大可达 1366X800 像素 (注: 实际的面板分辨率是取决于 pixel clock 与色深)

- QVGA: 320 x 240 x 16/18/24-bit LCD 屏幕

- WQVGA: 480 x 272 x 16/18/24-bit LCD 屏幕

- VGA: 640 x 480 x 16/18/24-bit LCD 屏幕

- WVGA: 800 x 480 x 16/18/24-bit LCD 屏幕

- SVGA: 800 x 600 x 16/18/24-bit LCD 屏幕

- QHD: 960 x 540 x 16/18/24-bit LCD 屏幕

- WSVGA: 1024 x 600 x 16/18/24-bit LCD 屏幕

- XGA: 1024 x 768 x 16/18/24-bit LCD 屏幕

- WXGA: 1280 x 768 x 16/18/24-bit LCD 屏幕

- WXGA: 1280 x 800 x 16/18/24-bit LCD 屏幕

- WXGA: 1366 x 768 x 16/18/24-bit LCD 屏幕

#### 2.6 显示功能

- 使用者可自行定义 4 个 32X32 图形光标

- 显示窗口

显示窗口大小是经由定义 LCD 寄存器得到,而透过底图 (canvas) 寄存器设定可以对显示窗口进行全部或部分更新。工作窗口的大小与起始位置的分辨率在水平上必须是以 8 个像素的倍数,以垂直而言则是 1 个扫描线的倍数。窗口的坐标参考原点为左上角(即使在翻转图像或旋转文字时,亦不需要主控端处理)。

● 虚拟显示

虚拟显示可用于显示大于 LCD 面板尺寸的图像。 图像可以在任何方向上轻松滚动。

● 画中画 (PIP)

支持两个画中画窗口,当使能画中画窗口时则画中画窗口会永远显示在主窗口中。画中画窗口的大小与起始位置水平上是 4 个像素的倍数,垂直上则是一条扫描线。透过设定画中画窗口的起始位置可以达成图像的滚动。 画中画 1 的窗口永远显示在画中画 2 上面。

● 多重缓冲区

多重缓冲允许在缓冲区之间切换主显示窗口。 缓冲区的数量取决于欲写入缓冲区的影像大小。 多重缓冲允许通过切换缓冲区来执行简单的动画显示。

● 唤醒显示

唤醒显示效果如果被使能时,那唤醒时可以快速显示预先储存在 SDRAM 中的显示数据。这个功能是在 Standby 与 Suspend 模式唤醒时使用。

● 水平/垂直翻转显示

水平/垂直翻转显示功能只适用在显示上,对于其它功能子方块的读写是不影响的,在垂直翻转显示使能时 PIP 是被禁能的。

● 彩条显示 (Color Bar Display)

在没有 SDRAM 的情况下仍然可以以彩条的方式显示, 预设分辨率为 640x480 像素。

#### 2.7 媒体解码单元 (MDU)

- 自动分辨 JPEG, BMP 和 AVI 格式。

- 支持 JPEG baseline profile,YUV444, YUV422, YUV420, YUV400,不支持 restart interval 格式。

- 支持带原始数据 (未压缩) 的标准 BMP 格式。

- 支持 AVI (motion JPEG) 视频显示。

- 提供 AVI 显示的自动播放、暂停和停止功能。

#### 2.8 区块传输引擎 (BTE)

- 2D BitBLT 引擎

- 具有光栅操作与颜色扩展的复制数据

- 方型填满与图样填满

- 提供使用者定义的 8x8/16x16 像素的图样

- 混合透明 (Opacity)

使用混合透明模式可以将两个图档混和成新的图形,然后再用画中画的方式显示出来。在处理的速度上而言混合透明与待处理图档大小有关,此外,亦可处理单张图档。

- 纯色抽离 (Chroma-keying) 功能: 经由指定的 RGB 颜色来做为透明的参考并进行混和影像的处理。

- 图形混合透明 (Alpha-blending): 根据寄存器设定透明的比率来进行两张图像的混成 (淡入与淡出功能必须被使能)。

- 像素混合透明 (Alpha-blending): 根据 RGB 格式来混合影像,例如 8bit RGB,则 MSB 2bit 为α值。

#### 2.9 几何绘图引擎

● 支持画点、线、曲线、圆、椭圆、三角形、矩形、圆角矩形

#### 2.10 SPI 主接口

#### 2.10.1 文字功能

- 内建 ISO/IEC 8859-1/2/4/5. 12x24

- 支持集通 16X16/24X24/32X32 串行字型 ROM 例如 Uni-code/BIG5/GB 等等,支持的集通型号有 GT21L16T1W、GT30L16U2W、GT30L24T3Y、GT30L24M1Z、GT30L32S4W、GT20L24F6Y、GT21L24S1W

- 支持使用者自定义字型半角 (8x16/12x24/16x32) 与全型

- 对于写入文字支持可程序文字光标

- 支持垂直水平放大字型 X1, X2, X3, X4 倍数

- 支持文字 90 度旋转

#### 2.10.2 DMA 功能

- 支持外部串行闪存 (serial flash) 数据复制至图框缓冲区

- 支援外部閃存 Signle/Dual/Quad mode

#### 2.10.3 一般主 SPI 功能

- 兼容 Motorola SPI 规格

- 16 bytes 读取深度的 FIFO

- 16 bytes 写入深度的 FIFO

- 在 Tx FIFO 完全清空并且 SPI Tx/Rx 引擎闲置时会发出中断

#### 2.10.4 IDEC 功能

- 支持外部串行闪存 (serial flash) 数据透過 MDU 至图框缓冲区

- 支援外部串行閃存 Quad mode

#### 2.11 IIC 接口

- IIC master interface

- 可以使用在扩充 I/O device,例如在屏幕控制的触控屏幕

- 支持标准模式 (100kbps) 与快速模式 (400kbps)

#### 2.12 脉宽调制与定时器

- 内建两个 16-bit 计数器

- 一个 8-bit pre-scalars 与一个 4-bit 除频

- 输出波形的工作周期是可程序化的

- 自动重加载模式或单击模式

- Dead-Zone 保护

#### 2.13 按键接口

- 支持 5x5 键盘 (必须使用与 GPIO 的共享脚)

- 可程序化的扫描周期

- 支持长按键与重复键

- 支持同时按两键

注: 在限制条件下可以支持同时按 3 键 (3 个键线段组成角度必须不是 90°)

● 支持键盘唤醒功能

#### 2.14 省电模式

- 支持3种省电模式

- 待机 (Standby)、休眠 (Suspend) 与睡眠 (Sleep) 模式

- 可以使用主控端、按键、外部事件唤醒

#### 2.15 频率来源

- 内建可程序锁相回路 PLL 以提供系统频率、LCD 扫描频率与 SDRAM 频率使用

- 单一石英晶体震荡输入: (XI/XO: 10MHz)

- 内部核心最大系统频率 (最大值 120MHz)

- SDRAM 频率 (最大值 166MHz)

- LCD 屏幕扫描频率 (最大值 100MHz)

#### 2.16 复位

- 接受外部硬件复位

- 软件命令复位

#### 2.17 电源

● I/O 电压: 3.3V +/- 0.3V

● 内建 1.2V LDO for core power

## 2.18 封装

- LQFP-100

- 操作温度: -40℃ ~85℃

## 3. 产品封装

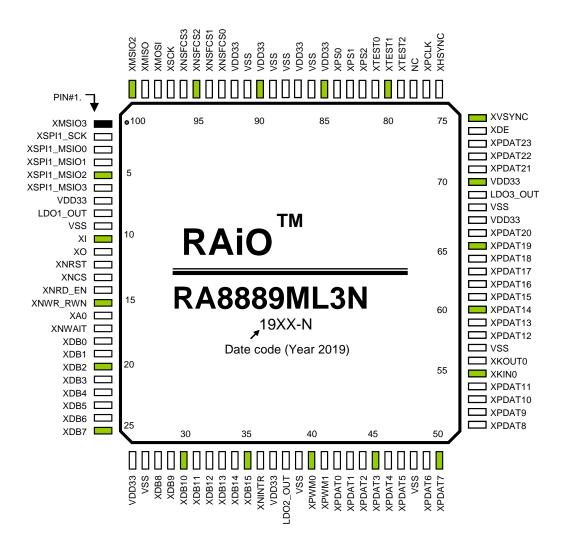

#### 3.1 RA8889 封装引脚图

Figure 3-1

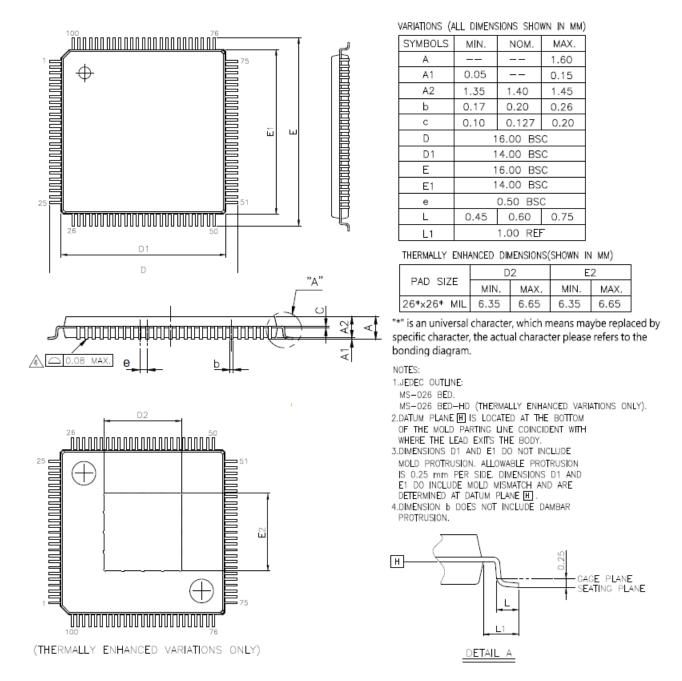

#### 3.2 封装尺寸

Figure 3-2: RA8889 Package Outline Dimensions

## 4. 引脚定义

## 4.1 并列主控端接口 (25 引脚)

| 引腳名稱      | I/O   | 引 腳 說 明                                              |

|-----------|-------|------------------------------------------------------|

|           |       | 数据总线                                                 |

|           |       | 数据总线提供主控端与RA8889 的并列接口数据传送。                          |

| V         | 10    | XDB[15:8] 可以设定GPIO (GPIO-A[7:0]), 前提是没有设定成 8080/6800 |

| XDB[15:0] | (8mA) | 16-bits并列接口数据总线。                                     |

|           |       | XDB[7:0] 如果在串行主控端模式下,此讯号也提供为串行的主控端信号使用,              |

|           |       | 请参考串行主控端接口章节。                                        |

|           |       | 命令/数据 选择                                             |

| XA0       | ı     | 此引脚被使用在选择命令还是数据的周期。                                  |

| AAU       | I     | XA0 = 0, 状态读取/命令写入。                                  |

|           |       | XA0 = 1,数据读取/数据写入。                                   |

|           |       | 芯片使能                                                 |

| XNCS      | I     | 低电平使能,如果主控端设定 RA8889 为串行主控端模式,则此引脚设定为                |

|           |       | GPI-B0 并且读取引脚的值,引脚内部有提升电阻。                           |

|           |       | 使能/读取使能                                              |

|           |       | 当微处理器是 8080 系列,此引脚是当作 XnRD 使用 (读取数据),低电平动作。          |

| XNRD_EN   | ı     | 当微处理器是 6800 系列,此引脚是当作 XEN 使用 (使能信号),高电平动作。           |

| (XEN)     | '     | 如果主控端接口设定成串行主控模式,那么此引脚则为 GPI-B1,并且可读取引               |

|           |       | 脚上的电压值。                                              |

|           |       | 内建提升电阻。                                              |

|           |       | 写入/读写                                                |

|           |       | 当微处理器接口是 8080 系列,此引脚会成为 XnWR (数据写入),低电平动作。           |

| XNWR_RWN  | ı     | 当微处理器接口是 6800 系列,此引脚会成为 XRnW (数据 读取/写入),读取           |

| (XRnW)    |       | 时是高电平动作,写入是低电平动作。                                    |

|           |       | 如果主控端接口是设定成串行主控模式,那么此引脚将会成为 GPI-B2。                  |

|           |       | 内建提升电阻。                                              |

| XNINTR    | 0     | 中断信号输出                                               |

|           | (8mA) | 告知主控端目前内部状态的中断输出。                                    |

|           | 0     | 等待信号输出                                               |

| XNWAIT    | (8mA) | 当 XnWAIT 为 high,表示 RA8889 已经准备好传输数据,当 XnWAIT 为 low,  |

|           | , ,   | 微处理器应该进入等待周期。                                        |

|           |       | 并列/串行 主控端接口选择                                        |

| XPS[2:0]  |       | 00X: (并列主控端) 8080 8/16-bits 数据总线接口。                  |

|           | I     | 01X: (并列主控端) 6800 8/16-bits 数据总线接口。                  |

|           |       | 100: (串行主控端) 3-wire SPI。                             |

|           |       | 101: (串行主控端) 4-wire SPI。                             |

|           |       | 11x: (串行主控端) IIC。                                    |

|           |       | <b>注</b> :                                           |

|           |       | 如果主控端接口设定成并列主控端模式,那么 XPS[0] 为外部中断接脚。                 |

## 4.2 串行主控端接口 (与并列主控端接口)

| 引腳名稱                     | I/O | 引 腳 說 明                                           |  |  |

|--------------------------|-----|---------------------------------------------------|--|--|

| XSSCL                    | I   | SPI 与 IIC 频率                                      |  |  |

| (XDB[7])                 |     | XSSCL、3-wire、4-wire 串行或 IIC 接口频率。                 |  |  |

|                          |     | IIC 数据/4-wireSPI 数据输入                             |  |  |

| XSSDI<br>XSSDA           | 1   | 3-wire SPI 接口: NC,请连接到 GND。                       |  |  |

| (XDB[6])                 | '   | 4-wire SPI 接口: XSSDI 串行接口数据输入。                    |  |  |

|                          |     | IIC接口: XSSDA 串行接口输入输出双向。                          |  |  |

|                          | Ю   | 3-wire SPI 数据/4-wireSPI 数据输出/IIC Slave 位置选择       |  |  |

| XSSD                     |     | 3-wire SPI I/F: XSSD,串行接口输入输出双向数据传输。              |  |  |

| (XDB[5])                 |     | 4-wire SPI I/F: XSSDO,串行接口数据输出。                   |  |  |

|                          |     | IIC接口: XIICA[5],IIC 设备地址 bit [5]。                 |  |  |

| V606                     | I   | SPI 使能/IIC Slave 地址选择                             |  |  |

| XnSCS<br>(XDB[4])        |     | XnSCS,在 3-wire 与 4-wireSPI 串行接口中,此引脚为使能信号。        |  |  |

| (312-[1])                |     | IIC 接口: XIICA[4],IIC 设备地址 bit [4]。                |  |  |

| XIICA[3:0]<br>(XDB[3:0]) | I   | IIC 接口: IIC Slave 地址选择                            |  |  |

|                          |     | XIICA[3:0],在 3-wire 与 4-wire SPI 接口: NC,请连接到 GND。 |  |  |

|                          |     | IIC 接口: IIC 设备地址 bit [3:0]。                       |  |  |

## 4.3 Serial Flash 或 SPI master 接口 (14 引脚)

| 引腳名稱    | 1/0                                                                                                                                                                                               | 引腳說明                                                                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| XNSFCS0 | IO<br>(8mA)                                                                                                                                                                                       | 外部 Serial Flash/ROM SPI 芯片选择 0<br>SPI 芯片选择接腳#0 使用在 Serial Flash/ROM 或 SPI 裝置選擇上。<br>*如果 SPI master 被禁能,那麼此引脚可以被程序規劃成 GPIO (GPIO-C3),预<br>设 GPIO-C3 为輸入功能。 |

| XNSFCS1 | 外部 Serial Flash/ROM SPI 芯片选择 1 SPI 芯片选择腳#1 使用在 Serial Flash/ROM 或 SPI 裝置選擇上。 * 如果 SPI master 被禁能,那么此引脚可以被程序规划成 GPIO (GPIO-C4) 预设 GPIO-C4 为输入功能。 *如果 xtest[2:1]不等於 01b 那麼在 reset 週期時會自动 pull-high。 |                                                                                                                                                           |

| XNSFCS2 | IO<br>(8mA)                                                                                                                                                                                       | 外部 Serial Flash/ROM SPI 芯片选择 2<br>SPI 芯片选择腳#2 使用在 Serial Flash/ROM 或 SPI 裝置選擇上。                                                                           |

| XNSFCS3 | IO<br>(8mA)                                                                                                                                                                                       | 外部 Serial Flash/ROM SPI 芯片选择 3<br>SPI 芯片选择腳#3 使用在 Serial Flash/ROM 或 SPI 裝置選擇上。                                                                           |

| хэск    | IO<br>(8mA)                                                                                                                                                                                       | SPI 串列时钟<br>此引脚是串列时钟輸出,主要是給 Serial Flash/ROM 或 SPI 裝置使用。 * 如果 SPI master 接口被禁能,那么此引脚可以被程序规划为 GPIO (GPIO-C0); 预设 GPIO-C0 为输入功能。                            |

| 引腳名稱             | I/O           | 引 腳 說 明                                                          |  |  |  |

|------------------|---------------|------------------------------------------------------------------|--|--|--|

|                  |               | 主輸出從輸入                                                           |  |  |  |

|                  |               | Single 模式: Serial Flash/ROM 或 SPI 裝置輸入資料用。對 RA8889 而言此腳          |  |  |  |

| VMOOL            | 10            | 为輸出。                                                             |  |  |  |

| XMOSI<br>(XSIO0) | IO<br>(8mA)   | Dual 模式: 此引脚为雙向資料傳送#0 (SIO0),此功能只能在 Serial flash DMA             |  |  |  |

| ( = = = ,        | (3)           | 使用。                                                              |  |  |  |

|                  |               | *如果 SPI master 接口被禁能,那么此引脚可以被程序规划为 GPIO                          |  |  |  |

|                  |               | (GPIO-C1); 预设 GPIO-C1 为输入功能。                                     |  |  |  |

|                  |               | 主輸入從輸出                                                           |  |  |  |

|                  |               | Single 模式: Serial Flash/ROM 或 SPI 裝置輸出資料用。對 RA8889 而言此腳          |  |  |  |

| XMISO            | IO            | 为輸入。                                                             |  |  |  |

| (XSIO1)          | (8mA)         | Dual 模式: 此引脚为雙向資料傳送#1 (SIO1)。此功能只能在 Serial flash DMA             |  |  |  |

|                  |               | 使用。                                                              |  |  |  |

|                  |               | *如果 SPI master 介面被禁能,那麼此引脚可以被程序規劃为 GPIO                          |  |  |  |

|                  |               | (GPIO-C2),預设 GPIO-C2 为輸入功能。                                      |  |  |  |

| V0100            | Ю             | 從輸入 IO2                                                          |  |  |  |

| XSIO2            | (8mA)         | Qaud mode: Serial Flash/ROM 或 SPI 裝置輸出資料用。對 RA8889 而言此           |  |  |  |

|                  |               | 腳为輸入。                                                            |  |  |  |

| VOICE            | IO<br>(8mA)   | <b>從輸入 IO3</b>                                                   |  |  |  |

| XSIO3            |               | Qaud mode: Serial Flash/ROM 或 SPI 裝置輸出資料用。對 RA8889 而言此           |  |  |  |

|                  |               | 腳为輸入。                                                            |  |  |  |

|                  | 10            | SPI 串列时钟 (SPI 1)<br>此引脚是串列时钟輸出,主要是給 Serial Flash/ROM 或 SPI 裝置使用。 |  |  |  |

| XSPI1_SCK        | IO<br>(8mA)   | * 如果 SPI master 介面被禁能,那麼此引脚可以被程序規劃为 GPIO                         |  |  |  |

|                  | (- )          | (GPIO-C0);預设 GPIO-C0 为輸入功能。                                      |  |  |  |

|                  |               | 主輸出從輸入 (SPI 1)                                                   |  |  |  |

|                  |               | 左軸山(旋軸)                                                          |  |  |  |

|                  |               | 为輸出。                                                             |  |  |  |

| XSPI1_MSIO0      | IO<br>(0 - A) | Dual 模式: 此引脚为雙向資料傳送#0 (SIO0),此功能只能在 Serial flash DMA             |  |  |  |

| _                | (8mA)         | 使用。                                                              |  |  |  |

|                  |               | *如果 SPI master 介面被禁能,那麼此引脚可以被程序規劃为 GPIO                          |  |  |  |

|                  |               | (GPIO-C1); 預设 GPIO-C1 为輸入功能。                                     |  |  |  |

|                  |               | 主輸入從輸出                                                           |  |  |  |

| XSPI1_MSIO1      |               | Single 模式: Serial Flash/ROM 或 SPI 裝置輸出資料用。對 RA8889 而言此腳          |  |  |  |

|                  |               | 为輸入。                                                             |  |  |  |

|                  | IO<br>(8mA)   | Dual 模式: 此引脚为雙向資料傳送#1 (SIO1)。此功能只能在 Serial flash DMA             |  |  |  |

|                  |               | 使用。                                                              |  |  |  |

|                  |               | *如果 SPI master 介面被禁能,那麼此引脚可以被程序規劃为 GPIO                          |  |  |  |

|                  |               | (GPIO-C2),預设 GPIO-C2 为輸入功能。                                      |  |  |  |

| 引腳名稱        | I/O         | 引 腳 說 明                                                |  |  |

|-------------|-------------|--------------------------------------------------------|--|--|

|             |             | 從輸出 IO 2 (SPI 1)                                       |  |  |

| XSPI1_MSIO2 | IO<br>(8mA) | Qaud mode: Serial Flash/ROM 或 SPI 裝置輸出資料用。對 RA8889 而言此 |  |  |

|             | ()          | 腳为輸入。                                                  |  |  |

|             | 10          | 從輸出 IO 3 (SPI 1)                                       |  |  |

| XSPI1_MSIO3 | IO<br>(8mA) | Qaud mode: Serial Flash/ROM 或 SPI 裝置輸出資料用。對 RA8889 而言此 |  |  |

|             | (=::::)     | 腳为輸入。                                                  |  |  |

## 4.4 PWM 接口 (2 引脚)

| 引腳名稱             | I/O         | 引腳說明                                           |  |  |  |

|------------------|-------------|------------------------------------------------|--|--|--|

|                  | IO<br>(8mA) | PWM 信号输出 1                                     |  |  |  |

| XPWM0            |             | XPWM 0 的输出模式可以在寄存器中指定。                         |  |  |  |

| XI WINO          |             | 如果 PWM 被禁能,那么此引脚可以被程序规划为 GPIO (GPIO-C7),预设     |  |  |  |

|                  |             | GPIO-C7 是输入功能或是输出核心频率。                         |  |  |  |

|                  | IO<br>(8mA) | PWM 信号输出 2 / 频率 3 输入(屏幕扫描频率)                   |  |  |  |

|                  |             | 当 XTEST[0]为低电平时:                               |  |  |  |

| VDVAVAA          |             | XPWM1 可以被设定为输出其输出模式可经由寄存器设定来完成。那么其输出           |  |  |  |

| XPWM1<br>(XCLK3) |             | 可以指定为标准的 XPWM1 功能,oscillator 频率输出或是 SCAN 频宽不足与 |  |  |  |

| (210 21 10)      |             | 超过内存地址的错误标志。                                   |  |  |  |

|                  |             | 当 XTEST[0] 为高电平时:                              |  |  |  |

|                  |             | XPWM1 引脚就是外部屏幕扫描频率 3 输入。                       |  |  |  |

## 4.5 键盘扫描 (10 引脚)

| 引腳名稱       | I/O                                      | 引腳說明                                       |  |  |

|------------|------------------------------------------|--------------------------------------------|--|--|

|            | I                                        | 按键数据或 GPIs (General Purpose Input)         |  |  |

| XKIN[4:0]  |                                          | 按键数据输入 (预设),内建 pull-up 电阻。                 |  |  |

| AKIIN[4.0] |                                          | XKIN[0] 具有 IIC master 的 XSCL 功能。           |  |  |

|            |                                          | In RA8889,XKIN [4:1] 与 XPDAT、GPIO-D 共享引脚。  |  |  |

|            | Keypad 闪控或 GPOs (General Purpose Output) |                                            |  |  |

| XKOUT[4:0] | 0                                        | Keypad 矩阵使用闪控扫描键盘,引脚上为 open-drain 输出 (预设)。 |  |  |

|            | (2mA)                                    | XKOUT[0] 具有 IIC master 的 XSDA 功能。          |  |  |

|            |                                          | In RA8889,XKOUT [4:1] 与 XPDAT、GPIO-D 共享引脚。 |  |  |

## 4.6 LCD 屏幕数字接口 (28 引脚)

| 引腳名稱   | I/O         | 引腳說明                                        |                    |              |                    |                    |         |

|--------|-------------|---------------------------------------------|--------------------|--------------|--------------------|--------------------|---------|

|        |             | 屏幕扫描频率                                      |                    |              |                    |                    |         |

| XPCLK  | O<br>(8mA)  | 屏幕扫描频率兼容于通用的 TFT 接口信号。                      |                    |              |                    |                    |         |

|        | (OITIA)     | 此信号为 SPLL                                   | 驱动产生。              |              |                    |                    |         |

|        | 0           | VSYNC Pulse                                 | <u>10.747 = 1</u>  |              |                    |                    |         |

| XVSYNC | (4mA)       | 垂直同步信号 V                                    | /SYNC 兼容·          | 于通用的 TF      | T接口信号。             |                    |         |

| XHSYNC | O<br>(4mA)  | HSYNC Pulse                                 | 10)410 米京          | C            | <b>-</b> k - k - 1 |                    |         |

|        | , ,         | 水平同步信号 <b>-</b>                             | ISYNC 兼谷           | 广迪用的 IF      | I 接口信亏。            |                    |         |

| XDE    | O (4m A)    | Data 使能                                     |                    |              |                    |                    |         |

|        | (4mA)       | 通用 TFT 接口的                                  | 的 data 有效或         | data 使能位     | 言号。                |                    |         |

|        |             | LCD 屏幕数据总                                   | 总线                 |              |                    |                    |         |

|        |             | 输出数据至 7                                     | ΓFT LCD 数          | (据总线,        | RA8889 可约          | 至由寄存器:             | 没定以支持   |

|        |             | 64K/262K/16.7I                              | M                  |              | 不同的设定法             | 医结相对应的             | RCB 总线  |

|        |             | 04102021010.71                              | W 凸/水, 及/I.        | 14 7 0 11 11 |                    | ESEAEV1) (777 H.1) | 八〇〇 心炎。 |

|        |             | Pin Name                                    |                    | Digital TE   | T Interface        |                    | ]       |

|        |             | TFT output                                  | 11b                | 10b          | 01b                | 00b                |         |

|        |             | Setting                                     | (GPIO)             | (16-bits)    | (18-bits)          | (24-bits)          |         |

|        |             | XPDAT[0]                                    | B0                 |              |                    |                    |         |

|        |             | XPDAT[1]                                    |                    | PIO-D1/ XKI  |                    | B1                 |         |

|        |             | XPDAT[2]                                    | GPIO-D6            | / XKIN[4]    | B0                 | B2                 |         |

|        |             | XPDAT[3]                                    | GPIO-E0            | B0           | B1                 | B3                 |         |

|        |             | XPDAT[4]                                    | GPIO-E1            | B1           | B2                 | B4                 |         |

|        |             | XPDAT[5]                                    | GPIO-E2            | B2           | B3                 | B5                 |         |

|        |             | XPDAT[6]<br>XPDAT[7]                        | GPIO-E3<br>GPIO-E4 | B3<br>B4     | B4<br>B5           | B6<br>B7           |         |

| XPDAT  | 10          | XPDAT[8]                                    |                    | PIO-D2/ XKI  |                    | G0                 | -       |

| [23:0] | IO<br>(4mA) | XPDAT[9]                                    |                    | O-D3/ XKO    |                    | G1                 |         |

| [23.0] |             | XPDAT[10]                                   | GPIO-E5            | G0           | G0                 | G2                 |         |

|        |             | XPDAT[11]                                   | GPIO-E6            | G1           | G1                 | G3                 |         |

|        |             | XPDAT[12]                                   | GPIO-E7            | G2           | G2                 | G4                 |         |

|        |             | XPDAT[13]                                   | GPIO-F0            | G3           | G3                 | G5                 |         |

|        |             | XPDAT[14]                                   | GPIO-F1            | G4           | G4                 | G6                 | ]       |

|        |             | XPDAT[15]                                   | GPIO-F2            | G5           | G5                 | G7                 |         |

|        |             | XPDAT[16]                                   |                    | O-D4/ XKO    |                    | R0                 |         |

|        |             | XPDAT[17]                                   |                    | O-D5/ XKO    |                    | R1                 |         |

|        |             | XPDAT[18]                                   | GPIO-D7/           |              | R0                 | R2                 |         |

|        |             | XPDAT[19]                                   | GPIO-F3            | R0           | R1                 | R3                 |         |

|        |             | XPDAT[20]                                   | GPIO-F4            | R1           | R2                 | R4                 |         |

|        |             | XPDAT[21]                                   | GPIO-F5            | R2           | R3                 | R5                 |         |

|        |             | XPDAT[22]                                   | GPIO-F6            | R3           | R4                 | R6                 |         |

|        |             | XPDAT[23]                                   | GPIO-F7            | R4           | R5                 | R7                 | J       |

|        |             | *未使用的引脚可以被程序规划成 GPIO-D/E/F(预设) 或 XKIN/XOUT, |                    |              |                    |                    |         |

|        |             | 预设是 18bpp 色                                 | 深模式,因此             | XPDAT[17:16  | 6/8:9/1:0] 预设      | 是 GPI 模式。          |         |

## 4.7 频率与复位与测试模式 (6 引脚)

| 引腳名稱          | I/O  | 引 腳 說 明                                            |

|---------------|------|----------------------------------------------------|

|               |      | Crystal 输入/Clock 1 输入(核心频率-core clock)             |

| VI            |      | Crystal Oscillator 必须是在 10MHz。                     |

| XI<br>(XCLK1) | I    | 当 XTEST[0]设为低电平时,此引脚是给内部的 crystal 电路使用,而此引脚应       |

| , ,           |      | 该连接外部 crystal 电路,这将可以产生 RA8889 的频率信号。              |

|               |      | 当 XTEST[0]设为高电平时,此引脚被拿来当作外部频率 1 输入。                |

| хо            | 0    | Crystal 输出                                         |

|               |      | 此引脚为内部 crystal 电路输出,而此引脚应该连接至外部 crystal 电路。        |

|               | I/OC | 复位输入信号                                             |

| XNRST         |      | 为了避免噪声产生错误的复位信号,外部复位信号的准位必须最少要有 256                |

|               |      | OSC 的频率周期。                                         |

|               | I    | 频率测试模式                                             |

|               |      | 内建 pull down 电阻                                    |

| XTEST[0]      |      | 此引脚是提供给芯片测试使用的,在标准操作上此引脚应该要连接至 GND。                |

|               |      | 0: 标准模式,使用内部 PLL 频率。                               |

|               |      | 1: 忽略 PLL, 芯片频率改使用外部 CLK1I、CLK2I、CLK3I 输入。         |

|               | I    | 芯片测试模式                                             |

| XTEST[2:1]    |      | 00: 标准模式。                                          |

|               |      | 01: 令 SPI master 引脚浮接 (使用在 in-system-programming)。 |

|               |      | 1X: 保留。                                            |

## 4.8 电源与接地

| 引腳名稱                             | I/O | 引 腳 說 明                         |  |  |

|----------------------------------|-----|---------------------------------|--|--|

| LDO1_OUT<br>LDO2_OUT<br>LDO3_OUT | Р   | <b>LDO 外接电容</b><br>外接 1uF 电容到地。 |  |  |

| VDD33                            | Р   | IO VDD<br>3.3V IO 电源输入。         |  |  |

| VSS                              | Р   | GND<br>IO Cell/Core 接地。         |  |  |